Khateb F, Khatib N (2011) New bulk-driven class AB CCII. Tonk A (2016) Short channel effects in conventional MOSFETs and their suppression. Int J Adv Res Comput Comun Eng 3(2):554–558 Tonk A, Goyal S (2015) A literature review on leakage and power reduction techniques in CMOS VLSI design.

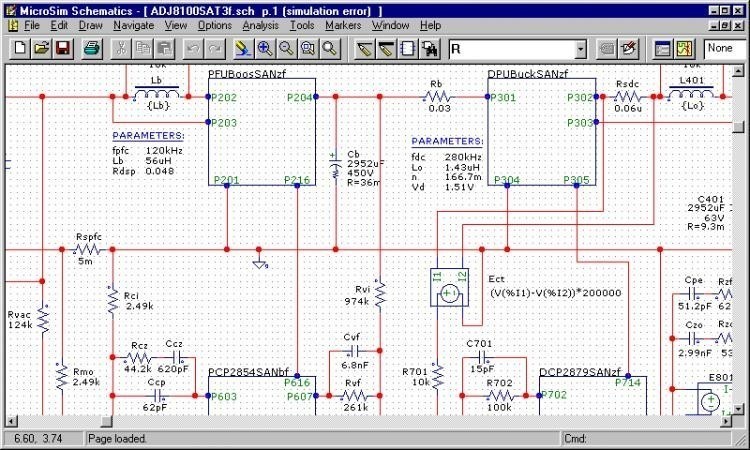

Khateb F, Dabbous SBA, Vlassis S (2013) A survey of non-conventional techniques for low-voltage low-power analog circuit design. Rajput SS, Jamuar SS (2002) Low voltage analog circuit design techniques. IEICE Trans Fundam Electron Commun Comput Sci 83(2):179–196 Yan S, Sanchez-Sinencio E (2000) Low voltage analog circuit design techniques: a tutorial. PSPICE simulations have been performed using 0.18 µm CMOS standard technology and obtained results confirm the theoretical analysis. These filters have been specifically designed for applications which involve extremely low-frequency operation like biosensors, bio-signal processing, etc. Further three voltage-mode filter configurations namely: a second-order band-pass (BP), band-elimination (BE) and high-pass (HP) have been implemented to verify the workability of the simulated high-valued inductance. The bulk-driven second-generation current conveyor (BDCCII) nearly allows rail-to-rail input-output operations while operating at supply voltage levels as low as ☐.5 V. This has been possible by incorporating an important non-conventional circuit design technique known as bulk-driven (BD) for implementing a second-generation current conveyor (CCII) cell. The paper presents the realization of a lossless grounded inductance circuit that is capable of low-voltage (LV) operations.

0 kommentar(er)

0 kommentar(er)